Q2 State Machine

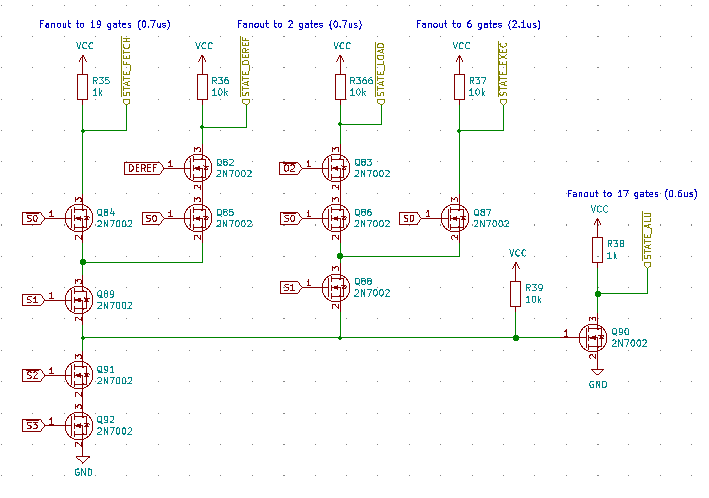

The state machine is advanced on the rising edge of the SC clock. There are 16 states. To reduce transistor count, the state machine is implemented as a 4-bit binary ripple counter. Since not all instructions use all states, the state decoder masks the DEREF and LOAD states if they are not used. The state machine rolls over without entering the ALU state if the ALU is not used. This means all instructions take either 8 or 32 cycles to complete depending on whether or not they use the ALU.

The states are:

- FETCH - Fetch the next instruction.

- DEREF - Dereference the operand if the dereference bit is set.

- LOAD - Load the operand from memory if this is an ALU instruction.

- EXEC - Execute the instruction or prepare the ALU.

- ALU - 12 states to run the 12 bits of A and X through the ALU.

The states are decoded using the followoing logic.

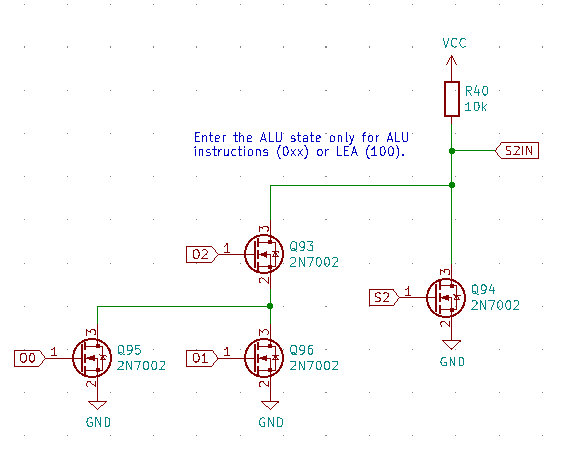

The S2 flip-flop input is gated using the following logic, which enables S2 only for instructions that use the ALU. All other flip-flops use their negated output as input to form a binary ripple counter.