Q2 RAM

The RAM for the Q2 is the one notable piece that is not implemented out of discrete transistors. The goal was to have a RAM that could save programs when powered off and be implemented without substantially increasing the size or power consumption of the Q2. A DRAM structure was considered (with large enough capacitors, DRAM will persist for a reasonable amount of time), but even that would require two transistors per bit, not to mention the address decoding logic and sense amplifiers. An actual core memory would be the most appropriate, but such things are hard to find, and the assembly of one does not appeal to me. So given that an off-the-shelf SRAM already provides exactly what we need, the Q2 goes that route.

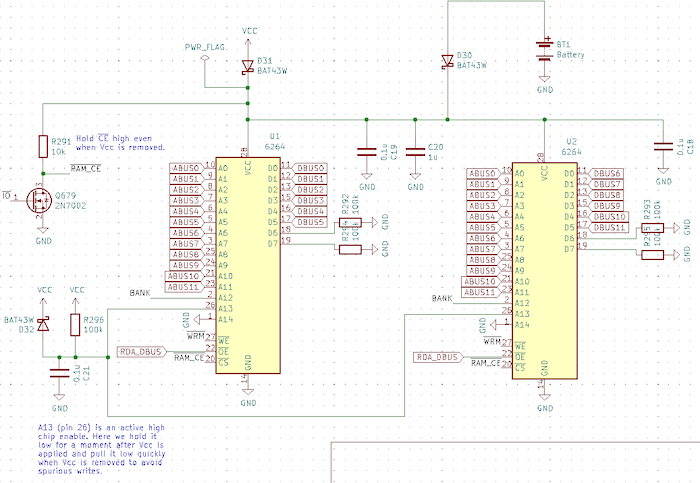

The RAM for the Q2 is provided by two 6264 SRAM chips. Each of these has an 8-bit data bus and a 13-bit address bus. Since we only need 12 bits for the data bus, two of the data pins on each are pulled to GND via 100k resistors. This provides a stable value for writes and low-current draw during reads. The extra address bit is connected to the memory extension device, allowing the Q2 to address 8190 words of memory as two fields (0xFFF is reserved for I/O in both fields).

An SRAM battery backup is provided for the SRAM to preserve any programs when the Q2 is not powered.

< Registers | Memory Extension >